# INTELLUNGEN

Ausgabe A

Nur für den Einstehnen

2-82

Grundzüge des höchstintegrierten Schaltkreisentwurfes (VLSI)

Minimierte Sendeleistung und Anwendung von Richtantennen in Funknetzen

# INSTITUT FÜR NACHRICHTENTECHNIK

Forschungszentrum des VEB Kombinat Nachrichtenelektronik

Aus urheberrechtlichen Gründen ist die Vertstlung des Heftes 2/1982 der INT-Mitteilung, Ausgabe A, auf den Bezieherkreis der INT-Mitteilung, Ausgabe B (Intern) beschränkt. Dieses Heft ist somit uur für den Dienstgebrauch im Kombinat Nachrichtenelektronik und seiner Kooperationspartner bestimmt.

INT-Pressestelle

Herausgeber: Institut für Nachrichtentechnik (INT)

Forschungszentrum des VEB Kombinat Nachrichtenelektronik, 1160 Berlin, Edisonstraße 63 Fernsprecher: 6380 Fernschreiber: INATE Berlin 112 637 Drahtwort: INATE Berlin

# **INT-MITTEILUNGEN**

# Ausgabe A

4. Jahrgang

1982

# Inhalt:

|                                        | Seite |

|----------------------------------------|-------|

| G. Heller                              |       |

| Minimierte Sendeleistung und Anwendung |       |

| von Richtantennen in Funknetzen        | 3     |

| esta fue des fotestatens sa fier       |       |

| G. Heinz                               |       |

| Grundzüge des höchstintegrierten       |       |

| Schaltkreisentwurfes (VLSI)            | 13    |

INT-Mitteilungen, Ausg. A 3 (1981)

Herausgeber: Institut für Nachrichtentechnik

DDR - 1160 Berlin, Edisonstr. 63

Tel.: 6381 0

Verantwortlicher Redakteur: Ing. Th. Reck

Schutzgebühr: 2,00 M

## G. Heinz

# Grundzüge des höchstintegrierten Schaltkreisentwurfes (VLSI)

Die technologisch mögliche Verkleinerung der Lateralabmessungen integrierter Transistoren auf Kanallängen > 2 um erschließt theoretisch bereits heute die Möglichkeit, mit einem durchschnittlichen Flächenbedarf 10 x 10 ,um2 pro Transistor (einschließlich der Anschlußleitungen) Schaltkreise mit 2,5 Millionen Transistoren auf einer Chipfläche von 250 mm² herzustellen. Perspektivisch werden es, kühnen Prognosen zufolge /11/, bis zu 109 Transistoren auf 1000 mm2 Chipfläche werden. Gegenwärtig wird an Schaltkreisen regelmäßiger Struktur mit etwa 700 000 Transistoren (512 k - dynam. RAM /11/) und an Schaltungen unregelmäßiger Struktur mit bislang typisch um 30 000 Transistoren (Spitzenwert: Hewlett Packard: 450 000 Transistoren /6/) gearbeitet.

Die Entwerfbarkeit bleibt in der Breite der Anwendungen hinter der Technologieentwicklung zurück.

Dieser Aufsatz beschreibt Mittel und Methoden dazu, die "Komplexitätsbarriere", d.h. die Grenze, an der eine Schaltung durch extrem hohen Aufwand nicht mehr ökonomisch und zeitlich effektiv zu integrieren ist, unabhängig von der jeweils vertretbaren "Komplexitätsbarriere\* weiter hinauszuschieben. Er ist Ergebnis eines Literaturstudiums. Ziel ist es, zu einer lebhafteren Diskussion effektiver Entwurfsmittel und -methoden für ISI- und VISI-Schaltkreise in der DDR-Fachliteratur beizutragen. Bislang beschränkt sich die Diskussion vornehmlich auf Technologie- und Simulationsfragen. Hartenstein /1/ erörtert, warum in naher Zukunft vor allem von den USA eine Inovationswelle hochintegrierter Kundenschaltkreise erwartet wird.

# Verursacht werden wird diese

durch die von Mead/Conway /2/ der Öffentlichkeit zugänglich gemachten Gedanken zum VISI-Entwurf; speziell zum top-down-Entwurfsstil;

- 2. auf Seiten der Technologie durch das vom Massachusetts Institute of Technology (M.I.T.) angeregte "Multi-University-Multiproject-Chip-Set-Project" (MPC) /1/, /2/ amerikanischer Universitäten;

- durch die Einführung interaktiver VISI-Layoutsoftware, so z.B. STICKS (interactives Stick-System), CALMOS (automatische Standardzellenverdrahtung) /14/;

- 4. durch die Schaffung schnellerer und leistungsfähigerer Simulatoren, wie Hybridsimulatoren (z.B. SPLICE), Timing-Simulatoren (z.B. MOTISC) und Mixed-level-Simulatoren /13/;

- 5. durch die Zusammenführung der genannten Softwarekomponenten mit Rückübersetzerprogrammen und gemeinsamer Datenbankverwaltung zur Realisierung kompletter und

effektiver VISI-Entwurfssysteme. Diese werden bei den gegenwärtig in Entwicklung befindlichen Schaltkreisen mit über 100 000

Transistoren bereits angewandt /6/, /14/,

/4/, /7/, /8/, /16/;

- durch die Einführung von VISI-Entwurfsplätzen auf Minicomputerniveau /7/, /8/, /21/.

Das Nachdenken über Mittel und Methoden des höchstintegrierten Entwurfes macht bestimmte Grundprinzipien deutlich, deren Beachtung auch den Entwurf von ISI- und MSI-Schaltkreisen erheblich effektivieren kann. Diese Grundprinzipien, ohne die ein VISI-Entwurf nicht denkbar ist, sind:

- alle Entwurfsschritte müssen zwar vom Menschen gesteuert werden, aber die Bearbeitung, Umsetzung und Auswertung der Datenmassen muß, um Fehlerfreiheit zu garantieren, maschinell erfolgen;

- sämtliche Software muß nicht nur vorhanden sein, sendern sie muß sich auch strukturell organisch und zeitlich optimal ins Entwurfsgeschehen eingliedern lassen;

3. die Entwurfsmethodik muß so gewählt werden, daß sie trotz technologischer Restriktionen (begrenzte Pinanschlußzahl, begrenzte Fläche, begrenzte Verdrahtbarkeit) schnell zu elektrisch wertvollen Layouts führt.

Gegenwärtig existieren verschiedene Methoden, höchstintegrierte Schaltkreise zu realisieren. Standardzellenkonzepte und Master-Slice-Techniken (vor allem bipolare Gatearrays) erlangen auf Grund der Möglichkeit, automatisierte Entwurfsverfahren anzuwenden, große Bedeutung. H. de Man /3/ schätzt die Layoutproduktivität im Vergleich zum "bristle block style" als zehnfach höher ein (aus /3/ geht nicht hervor, ob ein "bristle-block-style" im top-dawn-Vorgehen gemeint ist). Dennoch sind diese Techniken vor allem für den Entwurf teilweise regelmäßiger Strukturen (Speicher, Registerfelder) wenig geeignet. Sie sind zwei- bis zehnfach flächenintensiver /3/. Auf sie soll nicht eingegangen werden. Nur der top-down-Entwurfsstil schafft bislang die Möglichkeit, eine VLSI-Technologie "auszureizen". Er soll erörtert werden.

Folgerungen für die Erstellung von VISI-Hardund Softwaresystemen wie für die Entwicklung der Prüftechnik werden abgeleitet.

Der Artikel behandelt die VISI-Entwurfsmethodik, die zur von Hartenstein erörterten "Innovationswelle" auf dem VISI-Sektor, speziell auf dem der Kundenschaltungen, führen wird. Die zum effektiven VISI-Entwurf nötige Softwarebasis wird möglicherweise in einem folgenden Aufsatz ausführlich erörtert.

# Wozu VLSI?

Die Automatisierung der Produktion wird in den hochtschnisierten Ländern zur Tagesaufgabe.

Vollautomatische Fertigungsstraßen, elektronische Bildverarbeitung zur automatischen Fertigungsüberwachung, Ferndiagnoseverfahren für Werkzeugmaschinen und Zuwachs an Kommunikation bedingen höchstkomplizierte elektronische Schaltungen mit Hunderttausenden von Transistoren in einem riesigen Sortiment; also Schaltungen, die nur integriert mit kleinem Volumen, hoher Zuverlässigkeit und niedrigem Preis realisierbar sind. Als "Werkzeugmaschine" für den Entwurf derartiger Schaltkreise werden vor allem Tischrechner bzw. Minicomputer gi-

gantischer Leistungsfähigkeit in großer Stückzahl benötigt - ausgerüstet mit höchstintegrierten Schaltkreisen, weil nur mit den Leistungsmerkmalen: Dialogbetrieb, Datenverwaltung, niedriger Preis, interaktive Farbgrafik, Farbplotter, Printer und VISI-Software höchstintegrierte Schaltkreise (VISI) mit vertretbarem Aufwand an Zeit und Pinanzen realisierbar sind.

Es geht gegenwärtig international vorrangig darum, sohnell und effektiv mit schwerfälligen "Werkzeugmaschinen" hervorragende "Werkzeuge" zu entwickeln.

# Das Kernproblem - Fehlerfreiheit

Verallgemeinerbare Entwurfserfahrungen besagen, daß im manuellen Layoutprozeß (d.h. ohne Verwendung von Wiederholstruktursoftware) Fehlerzahlen in der Größenordnung der Transistoranzahl selbst entstehen.

Das sind etwa zu 95 \$ Zeichen- und Digitalisierfehler und zu 5 % elektrische Fehler. Zwar werden die 95 % der Fehler durch ein vorhandenes Topologieprüfprogramm angezeigt, aber Fehler können nicht subtraktiv entfernt werden. Mit oben genannten HP-Schaltkreis (450 000 Transistoren) würden ganze Entwerfergenerationen beschäftigt werden. Die Beseitigung von Fehlern bringt neue Fehler stets mit sich. Es obliegt den Qualitäten der Entwerfer, ihren Softwarehilfen und ihrer fehlerarmen Kommunikation, ob aus einhundert korrigierten Fehlern zwei oder zweihundert neue Fehler entstehen. Die Entwurfsmethode muß in erster Linie Fehlerarmut garantieren. Der Topologieentwurf muß frei von handgezeichneten Blementen sein. Für den elektrischen Entwurf gibt /2/ eine ganze Reihe von Forderungen an. Der VISI-

ganze Reihe von Forderungen an. Der VISISchaltungsentwurf muß hazardfrei vom Systementwurf bis zum Leyoutentwurf bleiben; dazu

gehört: eine weitestgehend synchrone Arbeitsweise lokal zusammenhängender Baugruppen

(finite-state machines), prinzipielle Pufferung an Schnittstellen mit asynchroner bergabe, Hazardvermeidung kombinatorischer Schaltungen durch Realisierung in kanonisch disjunktiver (bzw. konjunktiver) Normalform, rückwirkungsfreier Entwurf der Baugruppen. Asynchronität in VISI-Schaltkreisen kann z.B. die Folge von Taktausbreitungsproblemen sein /2/.

An die Softwareunterstützung des Entwurfes ergeben sich ebenfalls Forderungen:

Zeichen- und Digitalisierfehler sind von vornherein zu vermeiden.

Stickmethoden und automatische Standardzellenverdrahtung sind Voraussetzung für den Entwurf von VISI-Systemen. Die fopologieprüfung suß sofort nach der Digitalisierung des Layouts erfolgen (unter Engitalisierun wird die manuelle Leyoutüberführung in meschinenlesbare Form verstanden, unabhingig von den Hilfemitteln und der Ringabesprache). Lokal orientierte Topologieprüfprogramme bilden die Voraussetzung.

Ricktrische Fehler müssen erkennbar sein, Elektrische Fehler entstehen durch falsch verbundene Transistoren, fehlerhaft gesettte Kontaktfenster, durch fehlerhafte Übereinstimmung seischen System, Logik, Hetswerk und Leyout und durch fehlerhafte Elmensionierung der Bauelsmente.

Mückübersetsungsprogramme Layout - Metswerk bzw. Layout - Logik sind unverseidbar. De VISI-Schaltungan netswerknanlytisch komplett nicht beherrenber sind, andererseite aber mit höherer Abstraktionsstufe der Simulation (Logik-, Systensimmlation) deren Amessgekraft geringer wird, ergibt sich die Forderung nach Simulatoren, die Schaltungen gemischt in verschiedenen Beschreibungsarten (Sticklayout, Metswerk, Logik, System) behandeln können (mirsel-level-enmulation).

Wesentliohste Forderung des höchstintegrierten Entwurfes ist es, Entwurfsmetheden, Orgenisationsformen sowie Hard- und Softwareunterstützungen zu finden, die Pehlerquellen a priori ausschließen,

Zu diesem Komplex gehört auch die Frage, ob der Entwerfer die ihm angebotene Frogramstechnik nutzen wird.

VISI-Softwaresysteme mussen sich arbeitsorganisatorisch optimal in das Entwurfsgeschehen eingliedern lassen.

Schmelle Programme werden benötigt, auch schnelle Hintergrundrechner für Simulationen etc. werden gebraucht. Der Antwerfer will den Fortgang seiner Arbeiten am Risplay verfolgen. "Om line" Blalogbetrieb zum Entwurfenrbeitz-plats ist die Voraussetzung für eine effektive Asyouterstellung.

### Wer erstellt die Systemlösung?

Komplere Schaltungsstrukturen verlengen immense Systemkenntnisse, spesielle Prüf- und Meßtechnik, vie auch spesielle Systemsimulatoren. Die Einführung hochintegrierter Mikroelektronik Höft sich nicht von neuen Systemlösungen trennen. Die Systemspesialisten sind 1.4. in der Geritteindustrie zu finden.

Mit höherem Integrationsgrad ergibt sich somit ein prozentuales Anwachsen der Kundenentwürfe.

Die Systemlösung wird vom Geräteentwurf zum Bauelsmonteentwurf verschoben. Deraus muß sich zwangeläufig eine Verschiebung der Aufgeben der Buelementeentwicklung sum Geräteentwickler hin ergeben.

In /4/ wind s.B. betont, das sich mach veröffentilehten Amgaben der Firms VTI, Los Gatos, Kalifornien, USA, der Anteil von Rundementwürfen von weniger als 10 % im Jahre 1973 auf etws 50 % im Jahre 1976 erhölth hat, Rine 11neare Extrapelationsgerade würde auf den Anteil von 50 % an Kundementwürfen dieser Firms im Jahre 1989 hindewich

Pür kurse Technologiedurchlaufzeiten und kleine Pertigungestücksahlen

Die Ansahl der Technologiedurchläufe bei einer Schaltungsentwicklung ist begrenst. Die Entwicklung eines Schaltkreises maß vollsegen sein, noch ehe der Schaltkreis meraliseh versitet ist. Technologiedurchläufe kosten im Rahmen einer Schaltkreisentwicklung sehr viel Zeit. Gelingt es, die Technologiedurchlaufseit drastisch su verringern, erhöht sich die Ansahl der möglichen Technologiedurchläufe. d.h. höhere Fehlersahlen können korrigiert werden, des Entwicklungsrisiko sinkt, die "Komplexitätsbarriere" wird weiter hinausgeschoben. Mit ausnahme von Uriversalschaltkreisen ist nicht zu erwarten, daß mit höherem Integrationsgraden i.A. auch die Fertigungastuoksahl pro Schaltkreigtyp anwichst. Im Gegenteil. Edtig sind verstärkt technologische Verfahren und Arbeitsmethoden, die auch bei geringen Fertigungsstücksahlen angewandt werden könnan. Um nicht durch erhöhte Musterdurchlaufsahlen die Produktion anderer Bauelemente zu geführden, darf die Angahl und Große von Musterchargen nicht erhöht werden, mit dem . Multi-University-Multiprojekt-Chip-Set-Projekt" (KRC) /1/ amerikanisahar Universitten wird seit 1979 der Nachweis geführt, daß obige Forderungen erfüllbar sind. Hartenstein /1/ betont: "Es besteht die Gefahr, daß solche hochtechnielerten Ehnder (wie etwa die Ennderspublik), die sich dieser Bewegung nicht anschließen, sehr schnell ins Hintertreffen geraten können".

Hartenstein erläutert die Organisationsform ausführlich. Durch eine Elektronenstrahldirektbelichtung der Arbeitsmaske können die Maskendurchlaufzeiten drastisch verringert werden. Gleichzeitig lassen sich erst durch die B-Strahldirektbelichtung der Arbeitsmaske vorteilhaft Schaltkreise verschiedener Typen zusammen auf einem Chip integrieren. Beim MPC werden etwa 8 ... 10 unterschiedliche Schaltkreise pro Chip und etwa 8 unterschiedliche Chips pro Scheibe realisiert. Damit ist eine durchschnittlich siebzigfache (!) Stückzahlreduktion pro Schaltkreistyp bei gleicher Musterdurchlaufquote durch die Produktion erreichbar. Das MPC-Projekt wird seit kurzer Zeit in die Embargo-Regelungen der USA einbe-

Zukturtig ist eine Trennung zwischen dem technologischen Prozeß hochlutegrierter Schaltungen für kleine Stückzahlen (Kundenschaltkreise, Entwicklungsmuster) nach der MPC-Methode und für hohe Stückzahlen (Universalschaltkreise), basierend auf der Röntgenstrahllithografie, zu erwarten /2/.

### Trennung von Entwurf und Technologie - Aufgaben des Implementierungsätenstes Die Forderung nach Fehlerfreiheit im Entwurfs-

proces, wie auch das Problem des procentualen Anwachsens der Kundenentwürfe bedingen einfache Entwerfbarkeit mit einer exakten Schnittstelle zwischen Entwurf und Technologie. Das Entwurfungdienent wie auch die elektrischen Parameter von VISI-Eundentechnologien rücken in den Bereich von Industriestandards, Werden noch dazu verschiedene Schnitkreisprojekte auf einen Chip realisiert, so ist die

Die Forderung nach einer besseren Organisationsform der Schnittstelle wird beim NPC-Projekt durch Ausschreibungen eines sogen. "Implementierungsdienstes" gelöst. Zwischen Implementierungsdienst und Entwerfer besteht

verbindliche Festlegung der Schnittstelle un-

umgänglich.

kein Schriftwechsel, allenfalls Rundschreiben und leicht verständliche Hilfen mit Rezeptcharekter werden vom Implementierungedienst verschickt /2/, /1/. Be gilt, den Entwerfer frei von technologiespezifischen Aufgaben zu machen.

So ist es anstrebenswert, daß der Entwerfer einen von technologiespezifischen Aufgaben freien Datensatz definierten Formats an den "Implementierungsdienst" übergibt. Die Aufgaben:

- Umsetzen des Datensatzes in E-Strahl-Steuerdaten oder Paterndaten.

- Ebenenvorverzerrung.

- Hellfeld/Dunkelfeld-Rinstellung.

- Eintragen der Feinpositioniermarken, der Steprepeatmarken und der Technologiekontrollmarken usw.

mussen dem Implementierungsdienst überlassen werden. Im Falle des MEG-Frojekts // erfolgt die Trennung auf dem Kivau der Layoutbeschreibungssprache CIF 2.0, einer Sprache, deren Batei rechteckorientiert in Lambda-Entwurfargegin geschrieben wird.

Technologiespezifische Strukturen, z.B. die Eingangsschutzbeschaltung, können vom Implementierungsdienat bezogen werden. Es erweist sich als vorteilhaft, wenn durch den Implementierungsdienst nicht nur die Technologieschmittstelle verwaltet wird.

Mit einer VISI-Technologie ergibt sich die Notwendigkeit, Entwurfesoftware zu schaffen. Dies geschicht zweckmäßigerweise beim Halb-leiterhersteller, da nur er abschätzen kann, wann die nächste Technologieetappe erreicht wird, d.h. wann verbesserte Softwareysteme für höhere Entwurfekomplexität benötigt verden. So ist es bei VISI-Master-Slice-Systemen üblich, dem Kunden Verdrahtungesoftware zu verkaufen. Auch bei vom Kunden eigenständig entworfenen Schaltkreisen sollte das angestrecht werden. Der Kunde ist ohne VISI-Software hilflos. Für den Halbleiterhersteller ergeben sich völlig neue aufgebenbereiche.

### Die Bedeutung von Standardtechnologien wächst

VISI-Scheltungen zwingen zur Parellelarbeit von Entwerfern. Symbolische Layoutmethoden (z.B. STICKS) sind an technologiespezifische Unsetzerprogramme gebunden. Wolle Aufmerkeamkeit des Entwerfers muß dem Entwurfsprozeß angedeihen können, deshalb sind einfache und zeitlich unveränderliche Entwurfsrezeln anzustreben.

Zu einer breit anwendbaren VLSI-Technologie gehürt im Gegenestz zu bieherigen MSI- und ISI-Technologien ein teurer, technologiengesifischer Hintergrund, wie z.B.: Implementierungsdienst, Softwarepakete für Stickentwurf und autömatischen Standardsellenentwurf, Layout-Netzwerk-Bückübersetzer, Zellenbibliothek, Netzwerk-bw. Timing-Modellbibliothek und Hybrid-Modelle,

Der VISI-Hersteller wird in bisher unbekannten Maße auf eine oder wenige Technologien bzw. Technologievarianten festgelegt: Mit der Technologievahl seines ersten Schaltkreises wird der Hersteller von VISI-Schaltungen Über seinen Skonomischen Erfolg oder Mißerfolg der Zukunft wesentlich entscheiden.

Für den Halbleiterhersteller entstehen mit der VLSI-Technologie qualitativ völlig neue Aufgaben: Eine VISI-Technologie sollte deshalb s.B. über die Möglichkeit verfügen, extrem unsymmetrische Impulsfolgen mit minimaler Verlustleistung verarbeiten zu können, d.h. sie muß ermöglichen, statisch verlustleistungsfreie Gatter aufzubauen, die Impulse hoher Flankensteilheit erlauben. Integrierts Injektionstechnologien sind, obwohl sie das "ideale" YLSI-Layout haben, nur für Schaltungen geeignet, die ausschließlich mit annähernd symmetrischen Testverhältnissen arbeiten. Von einer VISI-Technologie wird hohe schaltungstechnische Flexibilität, verbunden mit möglichst einfach handhabbarem Layoutentwurf gefordert. Damit setzen sich Modifikationen der Technologien nSGT (einfaches Layout) und CMOS (höchste elektrische Flexibilität) für allgemeine ISIund VISI-Anwendungen durch.

Die Forderung nach statisch verlustleistungsfreien Gattern wird nicht zum "come back" der dynend sohen Techniken ihr Visi-Amendungen führen. Sohon auf Grund des entwurfeunglinstigen Layouts sind dynamische Techniken ungeeighet. Entscheidender Grund aber bleibt, einer Skalierungsbetrechtung Glassor's /z/ zufolge, der mit c<sup>-3</sup> abfallende Sigmal-Geräuschabstand zwischen zwei benachbarten Leitungen (cc : Skalierungsfaktor). Täktleitungen werden mit zunehmender Lestkepazität (d.h. mit einer großen Annahl zu versorgender Getes) zunehmende kritiech. Das Problem der Taktausbreitung wird in /2/ susführlich diskutiert. Von /2/ wird eine interessante lösung vorgeschlagen, Entwurfs- und Maskenkosten der nSGT weiter zu reduzieren. Vorausgesetzt, beide Kontaktfenstermasken haben gleiche Vorverzerrungawerte, läßt sich eine Maske einsparen. Palsch gesetzte Kontaktfenster sind hanfige Fehlerquellen, die nur durch Layout-Netzwerkrückübersetzungsprogramme sicher erkannt werden. Wird nur eine Kontaktfensterschablons erstellt, entfällt diese Fehlerquelle. Das Topelogieprüfprogramm muß einige Entwurfsregeln mehr prüfen, sowie in der Alu-Ebene über jeden "freien" Kontaktloch einen "butting contact" (Abdeckkontakt) generieren. Kain VISI-Schaltkreis wird ein restlos regelmäßiges top-down-Layout besitzen. Unregelmäßige, wilde" Logik muß einschränkungsles automatisch verdrahtbar sein. Laufzeiteffekte auf Polysil-Leitungen führen zu extrem komplizierten, schwerfälligen Programmen für die automatische Standardzellenverdrahtung, auch werden Entwurfsfehler provoziert. Abhilfe schaffen nur Metall-Leitbahnen. Im Falle des erwähnten 450 000-Transistorschaltkreises /25/ wird mit einer Polysil-Ebene (Transistorgates) und mit zwei darüberliegenden Wolframlagen unterschiedlicher Dicken (ca. 0,5 u und 1,2 u) und unterschiedlicher Entwurfsraster (unters Ebene: 2,0 um leitbahn und 1,0 um Abstand; obere Ebene: 5 um Leitbahn und 3,0 um Abstand) gearbeitet.

### Die Pinanschlußzahl ist bagrenst

Bedingt durch ein sich verschlechternies Verhältnis von Transistor- zu Minamschlußsahl und eine damit begrante Prüfmöglichkeit des Erstentwurfes steigt der Entwurfsaufvand progreselv mit der Pehlerennahl. Anf Pehlerefmulstionsprogramme und auf automatische Testatzgenerierung kann im VISI-Entwurf nicht mehr verzichtet werden. Um "schte-Pehler aus dem Teusenden von Pehlersimulationsprogramm angesedgten Pehlern seinnell und sicher herauszufinden, gewinnt der Einbau von Hardwaretesthilten am Bedeutung. Pir Zwecke der Pehlerenohe sind multiplezbers Pinamschillese annustraben. Pür Schaltungen mit stank soquentiellen Chursiter erscheidt s.B. der "Level-sensitive-soan-design" (ISSD) /22/, /23/ vorteilhaft. "Don't care"-Belegungen von Bussen sind vorteilhaft für Prüfzwecke verwendbar. Beingleigebend hierfür mag die von Johannsen in /2/ entworfene ALU sein. Die Prüfstrategle muß sich in den angestrebten Entwurfsstil einfügen lassen.

Die Forderung nach Prüfbarkeit des Entwurfes ist genau so wichtig, wie die Forderung nach Fehlerfreiheit.

Mit der Ansahl hintereinander liegender Ebenen innerer Zustände (Z) ebenso wie mit der Ansahl der Eingänge (X) wächst progressiv die Ansahl der zu testenden Fritfbelegungen an, (X + Z) stehen im Exponenten zur Besis Y, Y liegt zwischen eins und zwei, je nach Vermaschungsgrad der Verbindungslogik. Des ISSD-Verfahren ist der Versuch, das Netzwerk zu "entmaschen", inden jedem Flipflop als Paer innerer Zustände in fritfmode nur noch ein einziger Eingang zugerendet wird, und sämtliche Flipflops sohiebergisterartig hintereinander geschaltet werden. Die vermaschte Verbindungslogik allerdings bleibt als Eumpf übrig – sie muß mit anderen Methoden geprütt werden.

Die Müglichkeit, eine VISI-Schaltung "restlos" zu prüfen, existiert nur dann, wenn es gelingt, Verbindungslogik und Speioberregister vollständig zu prüfen (finite state maschine); eine solohe årbeitsweise ist anzutreben, ist aber 1.A. nicht durchfürbar.

Trotz Kinestz statistischer Prüfmethoden wird der Anteil der Prüfkosten am Produktwert progressiv mit dem Integrationsgrad anwachsen. Lange Prüfzeiten bedingen ein extremes Ansteigen installierter Prüftechnik bzw. wirken auf die Fertigungsstückzahl hemmend. Auf Grund dessen, daß die Absolutenzahl von Pinanschlüssen weiter ansteigt (200 ... 300 Pin-Gehäuse werden bereite erprott /9/), wichst die Bedeutung von Selbsttestverfahren und spezieller Prüftechnik. Universalprüfgeräte werden zu volumings.

### Warum abwärts gerichteter Entwurfsstil?

(Unter abwarts (top-down) gerichtetem Entwurfsstil wird die Positionierung des allgemeinen Verbindungsgraphen eines VISI-Schaltkreises beim Systementwurf verstanden.) Der hochintegrierte Entwurf ist ein inerstiver Prozes zwischen Logik-, Schaltunge- und Layoutoptimierung. Eine exakte, eindeutige Zuordnung zwischen Logik, Schaltung und Layout ist erforderlich. Es besteht die Forderung. Simulationsläufe ausgehend vom (u.U. fehlerbehafteten) Layout durchzuführen. Herkömmliche Arbeitsmethoden beruhten auf manueller Umformung der Datensätze zur Aufbereitung von Simulationsläufen. Die Aufbereitung von Daten für Simulationsläufe war extrem fehler- und arbeitsintensiv. Aktuelle Layoutkonfigurationen wurden nur teilweise berücksichtigt. In der Phase des Systementwurfes war es mit den klassischen Entwurfsmethoden wie Polyzellenentwurf oder Standardzellenentwurf kaum möglich, Rückwirkungen der Layoutkonfiguration auf die Schaltung von vornherein zu berücksichtigen, da i. A. die räumliche Anordnung der Baugruppen von vornherein nicht überblickt werden konnte.

Das ändert sich im top-down-Entwurfsstil. Laut Entwurfsphilosophie ist die räumliche Anordnung der Leitungen schon in der Systemebene festzulegen, erst dansch werden die Zellen gezeichnet. Um die räumliche Anordnung der Leitungen vorzunehmen, sind Stick-Layouts der Baugruppen Voraussetzung. Mit diesen Stick-Layouts stehen von vornherein aktuelle Simulationsdaten zur Verfügung. Durch die Methode des top-down-Entwurfes sind Schaltkreise zeitsparender und flächengünstiger zu entwerfen, als dies, vergleichbare Arbeitsweisen voraussetzt, mit der klassischen Polyzellenmethode möglich war. Mead/Conway /2/ betonen, daß der Entwurf des OM-2-Mikroprozessors von Johannsen /2/ (9000 Trs.) von drei Bearbeitern in einem viertel Jahr vollzogen wurde.

Der Entwurf des im top-down-Stil geschaffenen Hardwareassembler-Schaltkreises "SCHRME 79" (LISP-Dialekt, 10 000 Trs. /14/ dauerte von Beginn der Systemsimulation und Layoutbeginn bis zum Vorliegen erster getesteter Muster ein halbes Jahr /21/. An Softwareunterstützung waren vorhanden: ein Systemsimulator auf der Basis des Rechners PDP 10, mit dem der gesamte Befehlsablauf des Schaltkreises vor Arbeitsbeginn geprüft wurde; ein Mic code-PLA-Umsetzerprogramm; ein VISI-Layoutarbeitsplatz "ICARUS" (XEROX-PARC), ein Rückübersetzerprogramm Layout - Logik und ein Logiksimulator "MOSSIM", mit dem komplette Programmabarbeitungen des Schaltkreises nachgebildet wurden. Eines der ersten Muster funk-

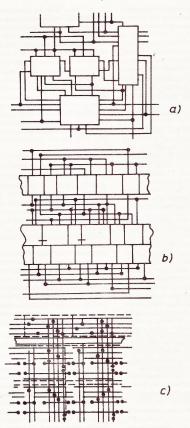

Tafel1 Entwurfsmethoden

- a) klassische Polyzellenmethode (engl./amerik.: building cells |14|) b) Standardzellenentwurf (engl./amerik.: standard cells oderpolycells/14|) c) top down Entwurfsstil (auch bristle block stile |2|)

tionierte bereits nach der ersten Präparation, an ihm wurden zwei die elektrische Funktion geringfügig beeinträchtigende Fehler festgestellt.

### Die Polyzellenmethode verändert sich inhaltlich

Die Ansehl handgeseichneter Elemente kann für den Entwurf höchstintegrierter Schaltkreise auf Grund der Forderung nach Fehlerfreiheit nicht wesentlich über das vom ISI-Entwurf übliche Maß hinaus gesteigert werden. Drei Auswege bieten sich an:

- a) Der Inhalt der Polyzellen muß durch die Verwendung von Logiketrukturen, die hierarchisch aufbaubere Loyouts provozieren, erhöht werden. (Bei Anwendung des Standardzellen-Entwurfsetile sollte diese Forderung ebenfalls Beachtung finden.) Demit wird zwar der Zellinhalt extrem komprimiert, aber die Vexdrahtung der Zellen untereinander bewirkt flächenzehrende Layouts bei alleiniger Anwendung dieser Methode.

- b) Nicht Transistoren, sondern Leitungen benötigen Flatz! Nicht Logikfunktioneblöcke, sondern Leitungen (Busse etc.) sind zu positionteren! Und dies bereits in der Systemsbene durch Feitlegung der gümnlichen Schnittstellen der Systemsbaugruppen. Me Folyzellen können i. A. erst nach vollzogenen Systementwurf erstellt werden (topdown-Entwurfestil). Nachteil des top-down-Entwurfestitle, Nachteil des top-downstruurfestitles, daß auf die in der Entwurfeblblichek des Entwerfers vorhandenen getesteten Folyzellen oftmals nicht zugegriffen werden kann.

- c) Ein erhöhter Aufwand für den Entwurf und die Simulation neuer Polyzellen muß deshalb bei Anwendung von b) akseptiert werden. Symbolische Leyoutherstellungsmethoden zur Verringerung der Leyoutarbeit, wie auch höhere Leyoutbeschreibungssprachen, die eine entwurfegünstige handhabbare gemeinsame Datenbank für Netzwerk, Logik und Leyout realisieren, und damit erfektivere vorab-Simulationen gestatten, sind anstrebenswert.

Beispiele für diesen neuen, abwärts ge-

Beispiele für diesen neuen, abwärts gerichteten, im wesentlichen durch Mead/ Conway /2/ artikulierten Layoutstil sind: die von Johannsen entworfenen OM-2-Layouts /2/, insbesondere die AlD; das Multiplizierfeld Hartensteins /4/, ein 16 x 16 Koppelfeld aus /20/, der SCHEMB-79-Frozessor aus /21/, und ein Mustererkenner /10/.

Da VISI-Schaltungen 1. A. einen hohen Anteil unregelmäßiger Strukturen, die zeitlich unkritisch eind, beinhalten, ergibt sich die Möglichkeit, den automatischen Standardzellenentwurf (für unregelmäßige Strukturen) mit den top-down-Entwurf (für regelmäßige Strukturen) zu kombinieren. Beispiele dafür sind das 450 000-Transistorchip von Hewlett-Packard /6/, /25/ und die 32-Mit-CFU von Bell /6/.

### Trots "Sticks" abwärts gerichteter Entwurfsstil?

wird angestrebt, den Entwurf mit Ein-Lambda-Entwurfsregeln ("Sticke"/2/, /14/) und entsprechender Softwareunterstützung aussuführen, sind die räumlichen Schnittstellen a priori im top-down-Entwurfsstil nicht exakt zu fixieren. Ein "Wandern" der Schnittstellen bedingt Zelldehnunge- und Zellkomprossionssoftware.

Die (auch symbolische) Entwurferegelprüfung muß während des Digitalisierens erfolgen, um dem Entwerfer die Möglichkeit bez. Unmöglichkeit des von ihm vorgegebenen Stick-Layouts in Besug auf benachbarte, bereits entworfens Layoutteile mitzuteilen. Interaktive, graphische Bildschirmtechnik ist Voraussetzung. Nur dadurch kann mit direkt digitalisierten Sticks ein zeit- und platzsparender top-down-Entwurf realisiert worden.

### Warum Lambda-Entwurfsregeln und Stickentwurf?

Kernproblem des Entwurfsprozesses ist und bleibt die Fehlerfreiheit. Wenn es gelingt, ein Layout-frundraster festsulegen, das größer als das übliche Mikrometerraster ist, so lässen sich Layoutfehler etwa um den Faktor der Rastervergrößerung vermindern. Gleichsettig sinkt die Fehlerrate der handgezeichmeten Strukturen betrüchtlich. Nach /2/ steigt die Fläche einer auf minimale Entwurferegeln nach der klassischen Folysellemsethode dimensionierten Polyzelle um maximal 30 5 bei Anwendung von Lambde-Entwurferegehn. Dieser Flächennuwechs wird durch die inhaltliche Veränderung der klassischen Polyzellenmethode zum top-dogmEntwurfestil mehr als kompenatert. Der Flächenzuwachs von 30 5 kann nicht gegen die Verwendung von Lambda-Entwurferegeln sprechen. Die Anwendung von auf um bew. auf Eruchfeile von um gerasterten, üblichen Entwurferegeln brächte in top-down-Entwurf kaum Flächensersparnis mit sich!

Softwareseitig ist es mit Lambda-Entwurfaregeln i. A. möglich, etws mit einem Zehntel der Genauigkeit auskurmen, Lambda-Entwurfsregeln erfordern nur Integer-Darstellung.

### Die "Entwurfsphilosophie" des top-down-Entwurfstiles

Ansatze allgemeingültiger Regeln für VISIfreundlichen Entwurf sind in /2/ zu finden. In /10/ und /1/ wird eine prägnante Zusammenfassung gegeben, die erweitert und präzisiert hier siedorgegeben werden soll:

- Leitungen statt Gatter sind zu positionieren

- die Daten sind busweise im "pipelining" zu bearbeiten

- die Parallelverarbeitungder Daten ist anzustreben

- elektrische Rückwirkungsfreiheit der Zellen ist anzustreben

- systolische Algorithmen der Datenbearbeitung sind anzuwenden

- der Steuersignalfluß sollte einfach und überschaubar bleiben

- geknickte Busse sind zu vermeiden

- wenige, einfache Zelltypen sind anzuwenden

- die Zellen sind lückenlos aneinanderzufügen

- die Zellen sollten hierarchisch aufbaubar sein

- für die Verdrahtungsebenen sind lokale Vorzugerichtungen zu wählen

- Langstreckenverbindungen sind zu vermeiden

- einfache Erweiterungsmöglichkeit ist anzustreben

- die räumliche Anordnung der Leitungen ist beim Systementwurf zu fixieren

- unregelmäßige Strukturen sind durch Maskenprogrammierung aus regelmäßigen Strukturen herzuleiten.

Unter systolischen Algorithmen (systolisch: pulsierend) sind hierbei nicht nur Algorithmenz zu verstehen, die den Datentrensport durch die Zelle in einer Richtung vollziehen. Ziel ist die räumliche und sequentielle Verhultung von Datenflässen aus unterschiedlichen Richtungen. So lassen sich Matrizoperationen hervorragend durch Prosessorfelder gleicher Zellen ausfähren, z.B. die IU-Zerlegung zur Lösung linesrer Gleichungseysteme mittels eines hermgonslen systolischen Prosessorfeldes /2/.

Die Zellularität der VISI, die bedingt wird durch mangelnde Entwerfbarkeit beliebig grefer Strukturen, führt zu neuen Maschinenarchitekturen. Hardwarereelisierte Assembler /21/ gewinnen an Bedeutung. Ein Zyklus-Feldoperationen (begronsten Fornate) eind denkbar. Arithmetisch extrem leistungsfähige Minicomputer werden in naher Zukunft erwartet - Computer im Tischformat mit der Leistungsfähigkeit der Großrechenanlagen in den Anfängen der Raumfahrt. Der technische Parameter "Schaltgeschwindigkeit" (des Getters)

wird gegen den nun beherrschbaren Parameter

"Schaltungskomplexität" ausgetauscht. "Zellularität" wird oberstes Entwurfeprinzip.

Für VISI-Entwurfssysteme auf Minicomputerbasis schlagen Foster und Kung /10/ die Verwendung von "Prüfmatrizen" zur Erkennung und Informationsreduktion aktueller Layoutkonfigurationen vor. Vermittels gekoppelter Prozessorfelder, durch die die aktuellen symbolischen Layoutdaten parallel in der einen Richtung "fließen", und durch die die aktuelle Erkennungsmatrix in der anderen Richtung "fließt", sind Layoutkonfigurationen durch VLSI-Prozessoren in Geschwindigkeiten erkennbar, die bisher hochleistungsfähigen Großrechnern vorbehalten blieben. Ein dafür möglicher Entwurf eines "pattern matchers" (Mustererkenners) wird in /10/ vorgestellt.

### Für eine einheitlich organisierte Datenbank

Mit wachsendem Integrationsgrad steigt die Möglichkeit, richtig zu simulieren, aber davon unbeeinflußt falsch zu entwerfen bzw. falsch zu simulieren, positive Krgebnisse zu erhalten, und wiederum falsch zu entwerfen. Und dies in den Ebenen des Systementwurfs (Register Transfer Level-RTL/3/), der Logikisimulation wie auch der Netwerksimilation. Wiederum steigt mit dem Integrationsgrad die Bünfigkeit derartiger Irrtimer. Steht die Entwicklung eines Schaltkreises dann noch unter Zeitnot, so kann die Komplexitätsbarriere proportional mit der Anahl der hinzugekommenen Entwerfer (auf

Grund von Kommunikationsfehlern) anwachsen!

Kernproblem ist also die Schaffung einer einheitlichen Datenbank für Simulations- und Topologiedaten. Erst damit steigt die Komplexitätsbarriere nicht mehr proportional der an einem Entwurf arbeitenden Entwerfer; mehrere Entwerfer können gleichzeitig an unterschiedlichen Teilen desselben Projektes arbeiten. Auf Grund dessen. daß diese Datenbank i. A. von mehreren Entwerfern angesprochen wird, ergibt sich aber ein weiteres Problem: diese Datenbank muß ständig aktuell sein bzw. es dürfen keine Belege dieser Datenbank existieren, die unaktuell sind, weil damit neue Entwurfsfehler provoziert werden! Die Datenverwaltung muß also vom Rechner ständig redigiert werden!

Schriftliche Belege sind im Entwurfsproses generell zu vermeiden. Deunt entfällt aus Skonomischen Gründen die Wöglichkeit, VISIlayoutsoftware ausschließlich auf Großrechnermiveau für den "closed-job"-Detrieb zu schaffen!

Eine auf <u>interaktive Displays</u> orientierte Arbeitsweise im "on-line"-Betrieb mit dem Rechner ist Grundvoraussetzung für jeden VLSI-Entwurf!

Mehrfachdateien müssen vermieden werden, sie führen im Entwurfsprozeß mit mehreren Entwerfern zu unlösbaren Kommunikationsproblemen und zur Störung der Harmonie des Entwurfsgeschehens. So würde allein eineLambda-Layoutdatei des erwähnten 450 000-Transistor-Schaltkreises von HP ca. 100 MByte (zehn Magnetbänder!) füllen. Käme noch eine Datei für Netzwerk- und Logikbeschreibung desselben Schaltkreises hinzu, würde jede Layoutänderung minutenlange Transformationsprogramme auf dem Hintergrundrechner zur Aktualisierung der anderen Datei bedingen, die Aktualität aller Datenbänke ist ja Voraussetzung für die Vermeidung von Kommunikationsfehlern! Effektiv kann nur mit einer Datei gearbeitet werden.

Miese Datei muß simtliche für Leyout und Simulationen nötigen Informationen beinhalten.

Um Rechenzeit zu sparen, muß die Datei in der Ebene angelegt werden, in der ständig gearbeitet wird: in der Layoutebene. Transnformationen zu höheren Entwurfesbenen (Netzwerk, Logik, RTL) müssen rechenzeitsparend erfolgen; der Umweg, Logikdaten über die Netzwerkrückübersetzung zu gewinnen, iet nicht effektiv. Die Charaktertiserung des Logischen Inhaltes eines Layoutabschnittes kann in top-down- wie im Standardzellenentwurf mit wenigen Ht erfolgen - einfashtentfalle wird die Layoutzelle mit den Namen ihrer logischen Funktion bezeichnet.

Der restliche Verbindungsgraph des Schaltkreises ist im top-down-Stil nicht vorhanden (laut Entwurfsphilosophie sollen die Zellen Hückenlos aneinanderfügbar sein - unvermeidbar übriggebliebene Leitungsstücke werden auch als Zellen definiert). Beim automatisohen Standardsellenentwurf ist er bereits auf einer Datei vorhanden.

### Die Identität zwischen den Entwurfsebenen ist herzustellen

Der Verbindungsgraph eines VISI-Schaltkreises ist in den Entwurfsebenen Maskenlavout. Sticklayout, Netzwerkbeschreibung und Logik sehr ähnlich. Der Grad der Ähnlichkeit bestimmt den Aufwand für die Überführung zwischen zwei Ebenen, ihre eineindeutige, eindeutige oder mehrdeutige Zuordnung. So ist beispielsweise die Transformation von Netzwerkebene in Logikebene bei Transfergatetransistoren, die in zwei Richtungen betrieben werden, oder bei bidirektionalen Bussystemen erheblich gestört, die Verbindungsgraphen sind unterschiedlich, die Ebenen Logik und Netzwerk sind mehrdeutig ineinander transformierbar. Bine Transformation ist aber nur dann "einfach", d.h. rechnergestützt möglich, wenn diese Stellen mehrdeutiger Interpretierbarkeit ausgeschlossen werden. Im allgemeinen schließt man die Gebiete mehrdeutiger Interpretierbarkeit in Zellen e: ., und nimmt die Überführung innerhalb der Zellen pauschal funktional (maschinell oder manuell) vor. Verbleibende Reste von Mehrdeutigkeit (bidirektionale Bussysteme) werden manuell transformiert bzw. auf die Überführung wird völlig verzichtet (mixed-level-simulation /3/).

Maschinell kann sinnvollerweise die Überführung innerhalb der Zellen nur über eine black-box-Beschreibung des Klemmenverhaltens der Zelle erfolgen. Dazu kann aus der vollständigen Netzwerksimulation der Zelle eine Tabellenbeschreibung des Übergangsverhaltens der Zelle als Prozedur generiert werden, die dem Logiksimulationsprogramm übergeben wird. Die Transformation Sticklayout - Netzwerk scheint speziell in den Polysiltechniken generell lösbar zu sein. Mit mengentheoretischen Ebenenverknüpfungen und einer "Informationsausfilterung" nach dem erwähnten "pattern-matching"-Verfahren /10/ bieten sich zeitlich effektive lösungsverfahren an. Möglicherweise wurden beim Entwurf des Rechners "Symbolics 3600" /7/ derartige Erkenntnisse bereits berücksichtigt. Die Überführung von Logik- in Systemniveau (RTL /3/) ist moglich, jedoch bereitet sowohl auf dem Systemniveau wie auch auf dem Logikniveau speziell die ausschließliche Anwendung zweiwertiger, d.h. Boolscher Algebra Schwierigkeiten. So kann die Ausbreitung von eingangsseitig eingesetzten don't-care-Termen (für den typischeren Fall einer noch fehlerbehafteten und unvollständigen Beschreibung) zu erheblichen Interpretationsproblemen für den Entwerfer führen.

### Wie wird der VISI-Arbeitsplatz aussehen?

Oben wurde bereits festgestellt, das die Layoutdstenmessen eines VISI-Schaltkreises nur in informationsreduzierter Form d.h. durch symbolisches Lambda-Layout für eine effektive Layoutarbeit geeignet eind. Die Umsetung in des Maskenlayout sollte zweckmissestung in des Maskenlayout sollte zweckmisseigerweise nur einmal, direkt vor der Maskenerzeugung und dann vom Implementierungsdienst vorgenommen werden. Unter Einbeziehung von Implementierungsdiensten braucht diese Umsetung nicht mit dem Entwurfsarbeitsplatz zu erfolgen.

Dem Trend zum Kundenentwurf hin muß durch leistungsfähige Minireohmer entsprochen werden, Bardwareassembler für eine VISI-Beschredbungssprache (Stickniveau) sind realisierbar und scheinen brauchbar zu sein /7/, /8/, /24/.

Die traditionelle Form des Entwurfsarbeitsplatzes wandelt sich geringfügig. Der Leyoutrechner wird mit Sticklayout und automatisoher Standardsellenverdrahtung bzw. mit online-Kommuniketion mit dem Entwerfer bei der Eingabe (Topologieprüfung) zunehmend belastet. Graphik-orientierte Layoutsysteme bringen ohnehin größere Hechnerbelastungen mit sich. Ein Trend zu Konfigurationen direkter Kopp-

Bin Trend zu Konfigurationen direkter Kopplung Display - Layoutrechner ist zu verzeichnen.

Schnelle Hintergrundrechner für Simulationen werden auch in Zukumft ihre Bedeutung behalten. Das Volumen der zu bearbeitenden Programme steigt, die Geschwindigkeit der Hintergrundrechner muß gestelgert werden, wesentliche Volumenreduktionen sind für Spitzensysteme auch in Zukumft nicht zu erwarten.

Die Perspektive deutet sich mit dem Hardund Softwarekonzept konsequent auf den VLSIEntwurf ausgerichtetem Minicomputer "Symbolics

5600" an /7/. Für die Verarbeitung der Sprache

"LISF" soll dieser Computer doppelt so schmell

sein wie der Großrechner VAX 780 und fast so

schmell, wie des DEG-System 20/60, Einige Daten: Hauptspeicher 1,125 MB bzw. 256 K für

32 bit-Worte; ausgestattet mit 64-Ebit-RAM's;

67 MB-Winchesterdisk; 1000 Zeilen-Display

(Farbdisplay in Entwicklung). Beginn der

Seriemfortigung: März 1982.

Wenn eingeschätzt wird, daß für die Hard- und Softwareentwicklung des Minicomputers fünf Jahre benötigt wurden, so kann angenommen werden, daß in den USA bereits seit acht Jahren Vorlaufarbeiten für die Schaffung leistungsfähiger VLSI-Entwurfsarbeitsplätze betrieben werden.

Das verwundert angesichte der Erfahrungen, die in den USA mit VISI-Entwurfssystemen herkömmlicher Art gemacht wurden, nicht. Der Konzern Hewlett Packard ist nach /14/ seit 1975 im Besitz eines (vollständigen) VISI-CAD-Entwurfssystems.

### Die Studentenausbildung muß "nachziehen"

Der Bedarf an speziellen Kundenschaltkreisen ist groß. Qualifizierte Entwerfer fehlen überall /1/.

Ziel des MRO-Frojekte ist zumächst vorrangig die Studentenausbildung, Man orientiert auf "konserative" Lambda-Entwurfsregeln ait  $\lambda = 2,5\,\mu\text{m.} \text{ auf Schaltungsoptimierung wird}$

nur dann Wert gelegt, wenn aus dem Prototyp ein Produkt werden soll.

Großen Stellensert nimmt das Vertrautmenhen mit büberen VISI-Beschreibungssprachen (AIDS, LAP, IGARUS) ein /1/. Hartenstein betont, daß es in den USA 1978 etwa 1000 - 2000 qualifizietes Entwerfer gab. Wird (vom autor) angenommen, daß mit jedem MRO-Projekt 300 Studenton ausgebildet werden, so ist mit einem erheblichen Zuwache an Entwerfern (und damit zumächst auch mit einer "Innovationswelle" auf den ISI-Sektor) zu rechnen.

Am M.I.T. (Messachusetts Institute of Technology) befaßt man sich bereits seit einigen

Jahren mit dem VISI-Zachrichtungen: Submikrometerstrukturen (< 1,um); Halbleitermaterialien; Halbleiterbauelemente; Halbleitertechnologie; Theorie der hochintegrierten

Schaltungen; VISI-Zachwurfsautomation; VISIKomplextitisteheorie und Schaltbreinserchitektur

innerhalb des "Departments of Electrica Engineering and Computer Science".

Pinamziert wird dieses Institut vor allem

durch Rüstungsaufträge /21/.

Studenten werden in die Auftragsvermittlung

einbezogen - von Betrieben delegierte Studenten werden bevorzugt. Sie werden sohriftlich

gebeten, sich Fachgebiete ihrer Interessen zu

wählen. Auch erfolgt die Ausbildung stark sepezialisiert und praxisorientiert - das Buch von

Mead/Conway /2/ wird als VISI-Iehrbuch angewennt.

### Zusamenfassung

Es wurde versucht, einen Einblick in die Vielfalt der VLSI-Entwurfsprobleme zu geben. Oberstes Prinzip des Entwurfes von VISI-Schaltungen sind fehlervermeidende Entwurfsmethoden im Layoutentwurf wie im elektrischen Entwurf: ein VLSI-Schaltkreis muß prüfbar sein. Der top-down-Entwurf wurde als layoutoptimale und zeitlich effektive Entwurfsmethode charakterisiert, unabhängig davon, ob er im Verbindung mit Lembda-Leyoutdarstellung in einem VISI-Layoutsystem für den Entwurf von ISI-Schaltkreisen, oder in Verbindung mit einer vollständigen VLSI-CAD-Softwarebasis auf Stickniveau für VISI-Schaltkreise Anwendung findet. Der Standardcharakter einer VISI-Technologie, der sich durch technologiespezifische Bibliotheken, Softwaresysteme und Implementierungsleistungen ergitt, wurde heruusgearbeitet. Die besondere Bedeutung von ersten VISI-Schaltkreisen für VISI-Entwurferechner als "Entwurfswerkzeuge" für eine breite und seitlich effekti 3 Schaffung von VISI-Schaltkreisen wurde erkennt.

Teilautomatisierte VISI-Entwurfsmethoden durch Anwendung des automatisierten Standardsellenentwurfseitle in Verhüdung mit einem stickorientierten top-down-Entwurf werden in Zukuntt die Voraussetzung für rationelle Layoutkompositionen bilden.

Die Tatsache, daß durch den VISI-Entwurf in Standardtechnologien Schaltungskomplexität gegen Arbeitzgeschwindigkeit der Technologie getauscht werden kann, wird zu neuen Bechnerrechttekturen führen. Die Schaffung einfacher Pormen "künstlicher Intelligenz" kann möglicherweise auf einen Zeitpunkt vor der Jahrtausendwende datiert werden.

Mein besonderer Dank gilt Herrn Dr. Zech für inspirierende Hinweise und für die Unterstützung der Literaturrecherche.

Herrn Dr. Bogk sei für kritische Durchsichten des Manuskripts und für helfende Diskussionen gedankt.

Nicht zuletzt gilt Herrn Dipl.-Ing. Krahl mein Dank für vielfältigste Anregungen und kritische Bemerkungen.

### Literaturverzeichnis

- /1/ Hartenstein, R.W.: VISI-Bausteine in geringen Stücksahlen für Spezial-Anwendungen. Elektronische Rechenanlagen, 22. Jahrg., 1980, H. 4, S. 159-173

- /2/ Mead, C.; Conway, L.: Introduction to VLSI-Systems. Addison - Wesley Publishing Company, 1980

- /3/ H. d. Man: CAD techniques for VISI. Europ. Conference on CAD, 1980, S. 243-248

- /4/ Report: About the Cover. IEEE Micro, May 1981, S. 5-7

- /5/ H.E. Jones; R.F. Schauer: An Approach to a Testing System for ISI. Symposium on Computer Aided Design of Eigital Electrone Circuits and Systems. Brüssel, 1978

- /6/ Proceedings of the IEEE, Oct. 1981, Vol. 69, No. 10, S. 1281-1304

- /7/ L. Waller: Lisp language gets special machine. Electronics, Aug. 25, 1981, S. 40-41

- /8/ R.C. Johnson: LISP System could speed mask making. Electronics, Aug. 11, 1981, S. 40-42

- /9/ J. Lyman: Packaging VLSI. Electronics, December 29, 1981, S. 66-76

- /10/ M.J. Foster; H.T. Kung: The design of Special-Purpose VLSI-Chips. IEEE Computer, Jan, 1980, S. 26-40

- /11/ F. Lohmann: Tendenzen der Größtintegration und der Bauelementeentwicklung. Elektronik, 25/26/1981, S. 51-65

- /12/ J. Allen; P. Penfield: VISI-Design Automation Activities at M.I.T. IEEE Transact. on Circuits and Systems, Vol. CAS-28, No.7, July 1981, S. 645-653

- /13/ H.de Man: Computer-Aided Design for Integrated Circuits - Trying to Brigde the Gap. IEEE Journal of Solid State Circuits, Vd. SO-14, No.3, June 1979, S. 613-621

- /14/ M. Marshall; L. Waller: VISI pushes super-CAD-techniques. Electronics, July 31, 1980, S. 73-80

- /15/ G.J. Sussman; J. Holloway; T.F. Knight: Computer Aided Evolutionary Design for Digital Integrated Systems. Mass. Institute of Technology, Art. Intelligence Lab.; AI Memo No. 526, May 1979

- /16/ J.C. Mudge; C. Peters; G.M. Tarolli: A VLSI Only Assembler. Proceed. of 1980 IBEE Int. Conference on Circuits and Computers, Port Chester, NT, USA

- /17/ S. Funatsu; N. Wakatsuki; A. Yamada: Designing digital circuits with easily testable consideration. Digest of Papers 1978 Semiconductor Test Conference, pp. 59-64

- /18/ Y. Crouzet; C. Lendrault: Implementation constraints in self-checking integrated circuits. ESSIRC 1979, Southampton, GB, S. 1-3

- /19/ G. Zweihoff; B. Könemenn, J. Mucha: Experimente mit einem Simulationsmodell für selbsttestende IC's. NTG-Pachberichte, 68, 1979, S. 105-112

- /20/ M. Snir: Orossbare 16 r 16. University of Edinburgh, Internal Report CSR-68-80/Sept. 80

- /21/ J. Holloway; G.L. Steele; G.J. Sussmann; A. Bell: The SCHEME-79-Chip. M.I.T. AI Memo No. 559, Jan. 1980

- /22/ E.B. Eichelberger: Method of Level Sensitive Testing a Functional Logik System. US-Patent No. 3761695, Sept. 25, 1973

- /23/ P. Foel; H. Lichas; T.E. Rosser; T.J. Stroh: LSSD Fault Simulation Using Conjunctive Combinational and Sequential Method. Proc. 1980 IEEE Test Conference, Cherry Hill, Nov. 11-13, 1980, pp. 371-376

- /24/ L. Lowe: VLSI tester runs at 50 MHz.

Electronics, Sept. 8, 1981, S. 212-214

- /25/ Digest of Papers of the IEEE International Solid State Circuits Conference, San Francisco, 1981, S. 104-107

- /26/ L.W. Summey: Sovernment Interest and Involvement in Design Automation Development The VBSIC Perspective.

18. Design Automation Conference, Proceedings, ACM IEES, Nahville, USA, June 1981, S. 344-346

### Begriffe:

- VISI: Very Large Scale Integration (dtsch.: Höchstintegration). Pro Chip werden 10 000 - 100 000 Logikgatter integriert.

- VHSIG: Very High Speed Integrated Circuits: Forschungsprogramm des US-Sekretariats für Verteidigungsforschung und Ingenieurwesen. Ziel ist es, VISI-Schaltkreise für auschließlich allitkrische Zwecke zu schaffen. Ein Programm, mit dem vorrangig die Entwurfauttometion forotext werden soll /26/.

- nsGT: n-Channel Silicon Gate Technique (dtsch: n-Kanal Silicon-Gate-Technik: Die Gateelektrode besteht bei modernen MOS-Technologien aus Polysilizium.

- EFC: Multi-University-Multiprojektchip-Set-Projekt: Projekt vorrangig sur Studentenausbildung, pro Silisiumscheibe werden bis su stebzig unterschiedliche Schaltkreise realisiert. Ein Implementierungsdienst des Halbleiterherstellers Übernimmt die Umsetzung von symbolischen Lambda-Layout in des Maskenlayout.

- STICKS:(dtsch: Stäbe): Programm zur Layoutsynthese aus dem symbolischen "Stäbchen"-Layout. Programm enthält Zelldehnungs- und Zellkompressionselgorithmen /14/.

- Master-Slice: (dtech: Meisterscheibe): Technik für kleine Serienstückzahlen. Beim Halbleiterhersteller liegen vorgefertigte "Master" ganzflächig metallisiert auf Lager. Der Kunde strukturiert nur die Leitbahnebene nach seinem Wunsch.

- Gatearray: (dtsch: Gatterfeld): Spezifizierte

Master-Slice-Technik in digitalen oder

in SGT-Anwendungen.

- Bristle-Block-Style: (dtsch: Borsten-Block-Stil)Butwurfsstil, der auf rechteckige, abgeschlossene Funktionsblockreslisierung im Layout hinzielt. Bedeutsam für Layoutsoftwarestrategie.

- Top-down-Style: Entwurfsstil, der dadurch gekennzeichnet ist, daß der Systementwurf

(top) von der Layoutrealisierbarkeit

(down) abhängig gemacht wird. Im Gegensatz dazu erfolgte bein traditionellen

Entwurfsvorgehen (LSI) der Systementwurf weitgehend getrennt von Layoutentwurf; nach dem Systementwurf wurde

die Logik entworfen, danach das Netzwerk, danach das Layout.

- Lambda-Entwurfsregeln: Vereinfachte Entwurfsregeln, mit denen es möglich wird, im top-down-style zu arbeiten, Entwurfsfehler zu vermeiden, und jegliche Layoutsoftwer rechenzeitspaream aufzubauen.

- Standardzellen: Zellen gleicher Höhe, die sich in Reihen angeordnet gut zur automatischen S.-zellenverdrahtung eignen.

- Lateralabmessung: (Lateral dtsoh: seitlich).

Der Knitwerfer arbeitet immer mit einer ihm (zumindest im Zielwerten) vorgegebenen Technologie. Diese bestimmt das Tiefenprofil, wie auch minimale Lateralabmessunen.

- On-Line: (dtsoh: auf der Leitung). Resistente Betriebsgystembestantielle im Hauptspeicher sichern, das der Programmierer (Entwerfer) in direktem Kontekt mit der Zentraleinheit steht. Damit wird schnellstwöglicher Zugriff auf den Rechner gewährleistet (Dialogmöglichkeit).

- Closed-Job: (dtsch: Stapelbetrieb). Um eine hohe Auslastung des Großrechners zu sichern, werden Programme (Jobs) geschlossen abgegeben und nacheinander abgearbeitet.

- Pattern-Matcher: (dtsch: Mustererkenner).

Bin kontinuierlicher betenstrom wird auf das Vorhandenesch bestimmter Daten und das Vorhandenesch bestimmter Daten muster geprüft. Damit bietet sich für Lambds-Layout eine zeitlich außerordentlich effektive Möglichkeit, schnelletmöglich z.B. Topologieprüfungen oder Netwerkrückübersetzungen durchsuführen.

- Integer: (dtsch: ganzzahlig). Integer-Operationen werden von einem Prozessor i.A. schneller ausgeführt als Fest- oder Gleitkommaoperationen.

- Mixed-Level-Simulation: (dtsch: Simulation in verschiedenen Entwurfsebenen). Um effektiv eimulieren zu können, ist es nütig, z.B. eine im layout vorhandene Schaltung mit noch nicht im Layout vorliegenden, nur durch ihre System-oder Logikbeschreibung vorhandenen Baugruppen zu verstüpfen.

- LISF: Höhere Programmiersprache (High-Jevel Langange), die beliebige Schachtelungen auflösen kann. Sie wurde auf Grund dessen, daß sie zu langesmen Programmen führt, bislang kaum angewandt.

- LSSD: (Level-sensitive-scan-design). Prüfverfahren für große, digitale Systeme, z.B. Großrechner. In das System wird zusätzliche Logik eingebaut, um eine bessere Prüfbarkeit zu erzielen /22/.

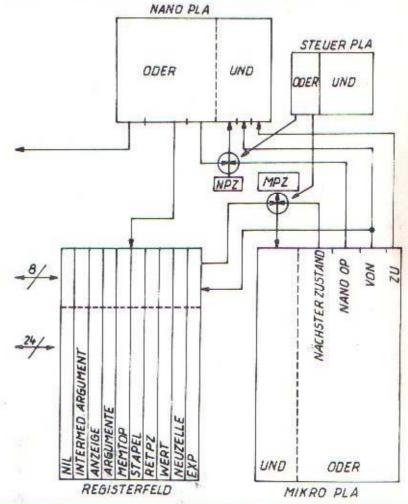

- Pinite-State-Machine: (dtsch: Festsustandamaschine). Jeder (große) Automat, deasen Ausgangsbelegungen zeitlich unsittelbar den Eingangsbelegungen folgen, kann aus einer mit Begistern beschalteten FLA synthetisiert werden. Dieser Gedanke ist ein Grundgedanke der Entwurfsautomstion und des top-down-Vorgehens. In weiteren Synthesschritten kann dieser in der RFL-Beschreibung vorliegende Automat in kleinere (zeitlich effektiver arbeitende) FLA's und Begister zerlegt werden.

- LU-Zerlegung: In der EDV übliches Verfahren zur Lösunge linearer Gleichungssysteme.

- PLA: Programmoble Logic Array (dtsoh: programmierberes logisches Feld): Layoutenordnung sur Realitierung eines in kenonisch-disjumktiver oder -konjumktiver Hormelform vorliegenden Boolschen Gleichungssystems, welches relativ stark mit dout-care-Termen belegt ist.

- RTI: Register Transfer Level (dtsch: Registersustauschebene). Höchste Abstraktionsebene einer VLSI-automatenbeschreibung nach Logik, Netwerk, symbolisches Layout und Maskenlayout.

seit

MIPC 78 seit MIPC 79

seit MPC 580

ab MPC 1280

M.I.T.

Caltech

Carnegie-Mellon-Univers.

Stanford University

U.C. Berkeley

U.O. Rochester

G.W.U.Washington, DC Kaiserslautern Univ. U.o. Ristol U.o. Colorado Springs U.o. Edinburgh U.o. Washington, Seattle Yale University

Tafel 2: Teilnahme am MPC Multi-University-Multiproject Chip Set Project (nach ///) U.C. Los Angeles

U.C. San Diego

U.o. Ilinois

U.o. Oslo, Norwegen

U.o. Santa Clara

U.o. Southern California

Washington U., St. Louis

Syracuse University