Dekan:

Dekan: Prof. Dr. rer. nat. habil. Werner Ebeling

(HU Berlin)

Ein wichtiger Verifikationsschritt beim Entwurf digitaler Schaltkreise ist die Logiksimulation, mit der logische und dynamische Fehler erkannt werden sollen. Aber MOS-Gatter besitzen keine konstanten Verzögerungszeiten. Diese schwanken erheblich in Abhängigkeit von der eingangsseitigen Flankensteilheit fe und der Belastung des Gatters (hier als auf die eigene Gatekapazität normierter Lastfaktor m).

Mead/Conway hatten 1980 in Ihrem Buch "Introduction to VLSI-Systems" einen Weg angedeutet, wie man die Dynamik hochintegrierter Schaltkreise besser kontrollieren kann ("Driving Large Capacitiv Loads", Seite 11 ff.). Diese Idee sollte für CMOS-Gatter untersucht werden.

In der Arbeit wurden mittels Netzwerksimulation Eigenschaften digitaler CMOS-Gatter aus dem Standardzellenkatalog U1500 (CSGT2, ZMD 1982) untersucht, mit der Zielstellung, dynamische Gattereigenschaften abstrahieren zu können, die eine genauere Wiedergabe der Dynamik bei der Logiksimulation ermöglichen können.

Siehe zur Einführung auch die Veröffentlichungen

GMS 1989 und

NTE 1990.

DISSERTATION

zur Erlangung des akademischen Grades

Doktor-Ingenieur (Dr.-Ing.)

vorgelegt der

Mathematischen-Naturwissenschaftlichen Fakultät

des Wissenschaftlichen Rates

der Humboldt-Universität zu Berlin

von

Dipl.-Ing. Gerd Heinz

Dekan:

Dekan:

Prof. Dr. rer. nat. habil. Werner Ebeling

(HU Berlin)

Gutachter:

Berlin, den 18.2.1988

Urkunde vom 17.5.1988

| ||

| Symbol- und Abkürzungsverzeichnis | 4 | |

| 1. | Vorwort | 8 |

| 2. | Statische Modellierung des CMOS-Inverters | 10 |

| 2.1. | Zweigeteiltes Transistormodell | 10 |

| 2.2. | Ungeteiltes Transistormodell | 14 |

| 2.3. | Approximation der Verstärkungsfunktion | 17 |

| 2.4. | Statisches Transferkennlinienfeld (STKF) | 21 |

| 2.5. | Statisches Gattermodell | 23 |

| 3. | Zeitfunktionen digitaler Flanken | 31 |

| 3.1. | Flankenformen | 31 |

| 3.2. | Taylorentwicklung | 34 |

| 3.3. | Integralkonstanz | 37 |

| 3.4. | Sinusförmige Meßflanke | 40 |

| 3.5. | Potentiale und Spannungen | 41 |

| 4. | Axiome der Gatterdynamik | 42 |

| 4.1. | Identität des Signalhubes | 42 |

| 4.2. | Bezugspotential | 43 |

| 4.3. | Flankensteilheit und Flankendauer | 44 |

| 4.4. | Spannungsverstärkung | 47 |

| 4.5. | Verzögerungsvektor | 48 |

| 4.6. | Nähe der Bezugspotentiale | 50 |

| 4.7. | Autonome Flanken | 51 |

| 4.8. | Flankenkonvergenz | 54 |

| 4.9. | Addition von Verzögerungsvektoren | 54 |

| 4.10. | Knotenkapazität und Knotenladung | 56 |

| 4.11. | Flankenstrom | 58 |

| 4.12. | Koppelkapazität | 60 |

| 4.13. | Kapazitäten invertierender Gatter | 61 |

| 5. | Kenngrößen invertierender CMOS- Gatter | 65 |

| 5.1 | Arbeitsbereiche des Gatters | 65 |

| 5.2 | Kenngrößen der Quasistatik | 68 |

| 5.2.1 | Inverterschwellspannung und -schwellstrom | 68 |

| 5.2.2 | Leerlaufverstärkung u. Ausgangswiderstand | 70 |

| 5.2.3 | Verzögerungszeit | 71 |

| 5.3 | Kenngrößen des Transitfalles | 73 |

| 5.4 | Kenngrößen der Sprungantwort | 74 |

| 5.4.1 | Schwellströme | 74 |

| 5.4.2 | Flankensteilheit | 74 |

| 5.4.3 | Flankenkonstante | 77 |

| 5.4.4 | Verzögerungszeit | 78 |

| 5.4.5 | Bestimmung der Millerkapazität | 81 |

| 5.5 | Zwischen Quasistatik und Sprungantwort | 85 |

| 5.5.1 | Verhältnis der Verzögerungszeiten | 85 |

| 5.5.2 | Länge der Übergangsbereiche | 86 |

| 5.6. | Relativität der Last | 88 |

| 6. | Dynamik invertierender CMOS-Gatter | 91 |

| 6.1 | Derzeitiger Erkenntnisstand | 92 |

| 6.2 | Untersuchungsmethodik | 94 |

| 6.3 | Simulationsbeispiel | 95 |

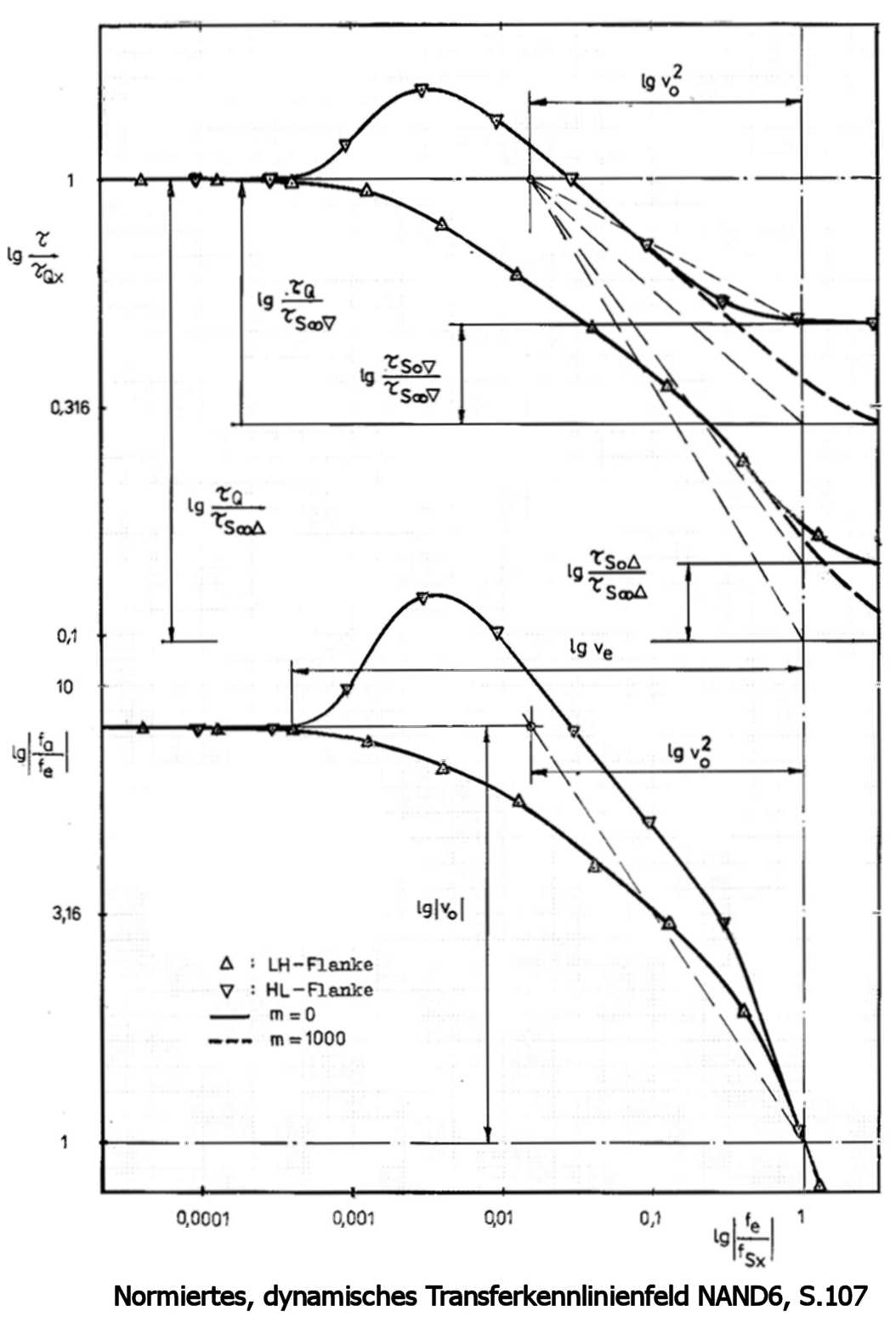

| 6.4 | Dynamisches Transferkennlinienfeld (DTKF) | 97 |

| 6.5. | Normiertes DTKF (NDTKF) | 99 |

| 6.6. | Länge des Übergangsbereiches | 104 |

| 6.7. | Unsymmetrie der Flanken | 106 |

| 6.8 | Iterativ lösbares NDTKF | 109 |

| 7. | Approximation der Gatterdynamik mit linearer Systemtheorie | 111 |

| 7.1 | Zeitverzögerung | 111 |

| 7.2 | Statische Überführungsfunktion | 113 |

| 7.3 | Faltungsmodell | 113 |

| 7.4 | Zeitkonstantenverhältnis | 115 |

| 8. | Zusammenfassung und Ausblick | 118 |

| 9. | Literaturverzeichnis | 120 |

| ANLAGEN | 145 | |

| 1. | NIFAN-Simulationsmodelle und -Prozeduren | 145 |

| 2. | Auswahl komplementärer Differenzen | 150 |

| 3. | Sinusförmige Meßflanke (EDGE) | 151 |

| 4. | Simulationsschaltung für NIFAN | 152 |

| 5. | Vergleich von Gatterkenngrößen | 153 |

| 6. | Gatterdaten SYNEG und NA6 | 154 |

| 7. | Berechnungsbeispiele | 155 |

| 8. | Betriebsspannungsabh. von Uinv und v0 | 157 |

| Erklärung | 158 | |

| Kurzfassung russisch | 159 | |

| Korrekturblatt |

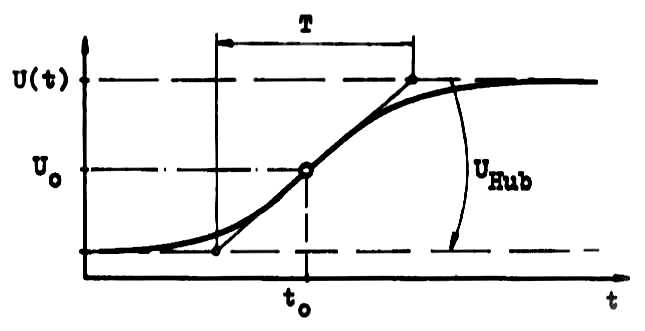

Flankensteilheiten f werden in der Arbeit normiert

auf den Signalhub UHub (i.a. VDD) eingeführt,

Flankensteilheiten f werden in der Arbeit normiert

auf den Signalhub UHub (i.a. VDD) eingeführt,

f = (du/dt) * (1/UHub)

Die so gewonnene, normierte Flankensteilheit hat die Maßeinheit einer Frequenz [1/sec = Hz]. Sie wird wie diese mit dem Symbol f bezeichnet.

Inverse der normierten Flankensteilheit ist die Flankendauer T = 1/f; siehe Kap.4, Seite 44 ff.

(bei Technologie CSGT2S: UHub = VDD = 5V)

Die Einführung der normierten Flankensteilheit ist die Voraussetzung, um DTKF und NDTKF einführen zu können und um im Rechenweg mit komplementären Differenzen arbeiten zu können.

Innovationen in dieser Arbeit sind:

und nicht zuletzt das Grundgesetz der Gatterdynamik (Kap.5.5.2):

Homepage www.gheinz.de

Mails to info@gheinz.de